要來開始介紹verilog跟一些他的基本的功能語法啦~

Verilog是一種硬體描述語言(HDL),很廣泛的被用在EDA(電子設計自動化),用來描述數字系統的結構及行為、設計電路等,常用在IC、微處理器、數位邏輯設備。

那Verilog有很多的部分,這大概會有好幾篇~今天就先來介紹如何開一個寫Verilog的檔案及組成Verilog的最基本構造-module。

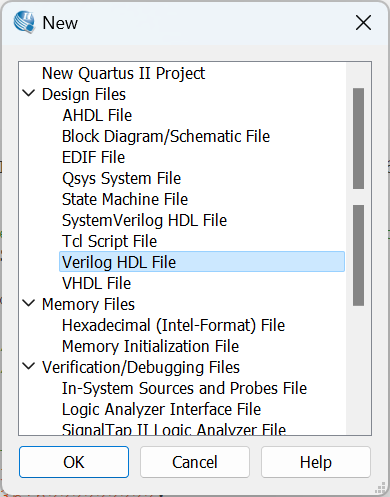

先來介紹一下在哪寫verilog,一樣利用Quartus建立好一個project後,開檔!到左上方的File,選New,然後選「Verilog HDL File」。

創立好檔案後,跟畫圖的部分一樣(如果還沒看電路圖用diagram表示的那篇,可以去看一下),要先記得修改檔名,到File,選Saved as,存好後到時候執行才不會有錯誤。

原本剛建立好,檔名應該會是「Verilog1.v」之類的。

修改好檔名後,上面的檔名應該會跟project name一樣。

接著就可以開始寫Verilog了~

首先要來介紹的是verilog的組成基本架構-module。

Verilog主要是由多個module組成,每一個module都描述了硬體特定部分。這些module是有階層的,其中會存在一個Top module。

Top module的名稱必須與project名稱一樣,否則執行時會出錯;Top module就像是C語言中的main,其他的module則是其他自定義的function。

每個module的大小都不同,可以用好幾個小的module組成一個大的module,例如Top module就可以由許多較小的module組成,這些較小的module可能又由幾個更小的module組成。

每一個module都有input、output及內部訊號。

module代表一個區塊的起始,結束這個區塊則是endmodule。

module基本結構大概是這樣:

module project_name(端口列表);

//端口類型宣告

//參數宣告

//內部邏輯指令

//模組功能使用、描述

endmodule

舉個小例子:

module newwork(A,B,F);

input A; //輸入端

input B; //輸入端

output F; //輸出端

assign F = A & B; //邏輯指令

endmodule //結束module

在input/output 後面接著的是使用到的變數名稱,這些名稱都要放在module之後的括號內,且結束後要記得加上「;」,接著就在底下宣告這些使用到的變數。

這裡跟C語言一樣,每個指令結束都要在最後面加上分號。但要注意,endmodule後面不用加上分號。

然後註解的部分,可以使用「//」或「/**/」來撰寫。

來稍微簡單提及一下module中的端口類型。

有了端口,就可以與外界交流囉~

那如果要在一個module內呼叫另一個module,只要寫上欲呼叫module名稱及輸入參數就可以了!

就像是C語言呼叫function一樣。

舉個簡單的例子:

module first(A,B,F);

input A;

input B;

output F;

Comb( A, B, F );

//其他內部指令

endmodule

module Comb(in1, in2, out);

input in1;

input in2;

output out;

assign out = in1 & in2;

endmodule

將主module的input及output訊號傳到Comb這個module,Comb將傳入的值做簡單的AND運算並將結果存在out中。

那今天就先到這邊~